Курсовая по микропроцессорам

Министерство высшего и профессионального образования РФ

Ижевский Государственный Технический Университет

Приборостроительный факультет

Курсовой проект

По дисциплине: техника микропроцессорных систем.

Тема: устройство управления на базе одно-кристальной микроЭВМ МС68Н705С8.

Выполнил студент-заочник: Дударев А.Ю.

Преподаватель:Марков М.М.

ИЖЕВСК 2001

Содержание.

1. Техническое задание.

2. Анализ технического задания.

3. Обоснование выбора элементов базы.

4. Описание электрической принципиальной схемы и ее работы.

5. Литература.

1. Техническое задание.

Разработать устройство управления на базе однокристальной микроЭВМ МС68Н705С8, содержащие следующие элементы:

1. Коммутатор аналоговых сигналов с напряжением от – 5 до + 5 вольт.

| Входы х выходы | 16х2 |

2. Оперативное запоминающее устройство (ОЗУ).

| Объем ОЗУ в байтах | 256 |

3. Постоянное запоминающее устройство (РПЗУ).

| Объем РПЗУ в байтах | - |

4. Аналого-цифровой преобразователь.

| Разрядность АЦП | - |

5. Цифро-аналоговый преобразователь.

| Разрядность ЦАП | 10 |

6. Входные дискретные сигналы.

| Количество входов | - |

| Наличие прерываний | - |

| Входные уровни | - |

7. Выходные дискретные сигналы.

| Количество выходов | 10 |

| Выходные уровни | ТТЛ |

8. Интерфейс обмена.

| Тип интерфейса | RS-232 9 выводов |

2. Анализ технического задания.

В ОЭВМ МС68НС705С8 (далее МК) имеется три порта общего назначения (по 8 линий ввода-вывода) и один специализированный порт (7 линий). Очевидно, что для непосредственного взаимодействия со всеми устройствами, входящими в состав разрабатываемого устройства управления (далее контроллера), этого количества линий недостаточно, т.е. по одним и тем же линиям ввода-вывода МК должен взаимодействовать с несколькими устройствами.

Исходя из выше изложенного, на портах МК необходимо организовать три шины: данных, адреса и управления, а в состав внешних устройств должны входить регистры, в которые по шине данных с помощью сигналов шины управления будут записываться необходимые данные.

Рассмотрим особенности построения каждого из внешних устройств.

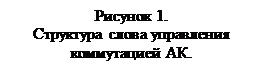

Коммутатор аналоговых сигналов должен состоять непосредственно из самого аналогового коммутатора и регистра, в котором будет записываться слово управления коммутацией. Для выбора одного из 16-ти входов требуется 4 разряда управляющего слова, для выбора одного из двух выходов необходим один разряд, целесообразно так же выделить один разряд для отключения обоих выходов. Таким образом, слово управления аналоговым коммутатором содержит 6 разрядов. Для записи данных в регистр управления требуется один сигнал управления.

Т.к. емкость ОЗУ невелика (256 байт) целесообразно применить статическое ОЗУ, чтобы исключит схему управления динамическим ОЗУ. Схема ОЗУ должна предусматривать отключение от шины данных, т.к. к ней подключены и другие устройства. Сигналы взаимодействия с ОЗУ состоят из 8-ми адресных разрядов, 8-ми разрядов данных и двух сигналов управления- сигнала чтения/записи данных и сигнала отключения выводов данных.

Блок цифро-аналогового преобразователя содержит непосредственно сам ЦАП со схемой формирования опорного напряжения и регистра хранения цифрового кода. Для управления ЦАП требуется 10 разрядов кода и один разряд сигнала записи кода в регистр хранения.

Схема выдачи дискретных сигналов должна состоять из регистра выходных сигналов и схемы преобразования к уровням ТТЛ, если последняя потребуется, в зависимости от применяемого регистра. Для выдачи дискретных сигналов требуется 10 разрядов самих сигналов и одного сигнала управления регистром.

Для организации последовательного интерфейса RS-232 целесообразно использовать встроенный в МК последовательный интерфейс связи, используя его линии RDI, TDO как сигналы RxD, TxD соответственно интерфейса RS-232. Оставшиеся 4 входных сигнала интерфейса RS-232 можно подавать на линии порта D МК, а для двух выходных сигналов управления интерфейсом RS-232 требуется использовать регистр хранения, записывая в него сигналы с шины данных. Для преобразования друг в друга уровней стандартных сигналов интерфейса RS-232 (низкий уровень –15…-5В, высокий +5…+15В) и КМОП 5В необходимо применение схем согласования.

Для исключения постоянного опроса входных сигналов управления интерфейса RS-232 целесообразно организовать прерывание работы МК по изменению этих сигналов.

Таким образом, шина адреса должна быть 8-ми разрядной (ОЗУ), шина данных 10-ти разрядной (ЦАП, выходные дискретные сигналы), шина управления 6-ти разрядной (1 разряд - аналоговый коммутатор, 2 - ОЗУ, 1 - ЦАП, 1 - дискретный выходной сигнал, 1 - RS-232).

Итак, можно перейти к выбору элементной базы и составлению принципиальной электрической схемы.

3. Обоснование выбора элементной базы.

Т.к. МК реализован по КМОП - технологии и использует напряжение питания 5В, то целесообразно и другие микросхемы выбрать КМОП типа с напряжением питания 5В, для исключения схем согласования уровней и уменьшения энергопотребления.

Наиболее приемлемыми по быстродействию и нагрузочной способности являются КМОП микросхемы серии КР1554, поэтому выберем все неспециализированные ИС из этой серии. В качестве регистра хранения выберем ИС КР1554ИР23 – 8-ми разрядный регистр хранения с синхронизацией по положительному фронту тактового сигнала. В качестве регистра хранения двух и менее разрядов целесообразно применить ИС КР1554ТМ2 – два D - триггера с синхронизацией по положительному фронту тактового сигнала. Микросхемы комбинационного типа также используем серии КР1554.

Для коммутирования входных аналоговых сигналов используем ИС КР590КН1 – аналоговый коммутатор 8х1 со встроенным дешифратором коммутации и входом разрешения коммутации. Для коммутирования выходных аналоговых сигналов применим ИС КР590КН5 – четыре управляемых аналоговых ключа. Обе микросхемы позволяют коммутировать сигналы напряжением –5…+5 и управляются уровнями КМОП 5В, чем и обусловлен наш выбор.

Исходя из анализа, ТЗ в качестве ОЗУ целесообразнее выбрать статическое ОЗУ с отключением выводов данных, также желательно, что бы ИС ОЗУ имела объединенные входы/выходы данных, количество входов было бы равно 8-ми (чтобы использовать один корпус), емкость не менее 256 байт и входные/выходные сигналы с уровнем КМОП 5В. Этим требованиям отвечает ИС К537РУ9А – статическое ОЗУ с построением 2Кх8.

В качестве ЦАП целесообразно применить ИС ЦАП со встроенным регистром хранения входного ряда, а т.к. требований к быстродействию не предъявлено, применим ИС КР572ПА2А – 12-ти разрядный ЦАП с входными регистрами хранения.

Для формирования выходного сигнала ЦАП, а также для схемы формирования выходных уровней интерфейса RS-232, требуются быстродействующие ОУ, такие как КР574УД2А – два ОУ со скоростью нарастания выходного сигнала 50В/мкс.

Очевидно, контроллер входит в состав более сложного устройства, т.е. плата контроллера подстыковывается к плате соединений, таким образом, целесообразно применить одну розетку для печатного монтажа, такую как трех- рядная 72-х контактная РПМ7-72Г-П-В.

4. Описание схемы принципиальной электрической и работы схемы.

Центральным устройством схемы контроллера является МК DD9. На портах общего назначения DD9 организованы: шина адреса А7..А0 (линии РА7..РА0), шина управления внешними устройствами (РВ5..РВ0) и шина данных D9..D0 (линии РВ7, РВ6, РС7..РС0).

Внешний сигнал начальной установки (RESET) DD9 не предусмотрен, т.к. в нем нет необходимости; при подаче напряжения питания происходит RESET по включению, а при сбоях программы можно предусмотреть по сигналу СОР – таймера.

Рассмотрим построение и работу каждого из внешних устройств.

1) Коммутатор аналоговых сигналов (АК).

АК входных сигналов построен на двух восьмиканальных коммутаторах DD6, DD7, выходы которых обьединены и подаются на входы двух ключей DD8 , выходы которых и являются выходами АК.

Режим коммутации определяется управляющим словом, записанным в регистр DD5, структура слова управления представлена на рис.1.

Слово управления АК записывается в регистр DD5 следующим образом:

на линии D5..D0 (РС5..РС0) МК выставляет логический “0”, и последний сигнал АС переводится в высокий уровень, таким образом данные с линий D5…D0 по положительному фронту сигнала АС записываются в регистр DD5.

2) Интерфейс RS-232.

Для организации интерфейса RS-232 использован встроенный в МК последовательный интерфейс связи. Вход приемника RS-232 (RxD) через преобразователь уровней (работу которого рассмотрим ниже) подключен к соответствующему входу МК RDI, а выход передатчика МК TDO через преобразователь уровней (ПУ) подключен к входам порта D MK (PD2…PD5 соответственно), а выходные сигналы RS-232 записываются МК в регистр хранения DD11, с выхода которого через ПУ подаются на соответствующие входы RS-232.

Запись выходных сигналов управления RS-232 (DTR, RTS) в регистр DD11 происходит следующим образом:

МК выставляет на линии D8, D9 требуемые уровни сигналов DTR, RTS , а на линии INT (PB5) низкий уровень, затем сигнал INT переводится в «1», по положительному фронту сигнала INT данные D8, D9 записываются в регистр DD11 и выдаются на его выходах и соответственно на выходах RS-232.

Как следует из анализа ТЗ в схеме организовано прерывание по изменению входных сигналов управления RS-232. Рассмотрим формирование сигнала прерывания IRQ на примере сигнала DCD:

Сигнал DCD после ПУ подается на вход элемента «исключающее или» DD3.1, на другой вход DD3.1 подается этот сигнал через диффиринцирующую цепь R11C1, т.е. при изменении сигнала DCD на втором входе сигнал изменится только через время t = 0,7R11C1, таким образом на это время на выходе DD3.1 будет сигнал высокого уровня, который через элементы ИЛИ DD4.1, DD4.3 и проинвертировавшись на DD2.2 подается на вход IRQ МК, тем самым вызвав прерывание выполнения основной программы и переход к подпрограмме обработки прерывания. Аналогично формируется сигнал прерывания от других входов RS-232, RI, DSR, CTS.

Выбор времени t = 0,7 · 100кОм · 470пФ = 33мкс произведен из следующих соображений:

МК должен принимать сигнал прерывания как по фронту так и по уровню; во время обработки внешнего прерывания МК не реагирует на другие запросы внешнего прерывания, вызванные изменением другого сигнала управления, а т.к. изменение уровня другого сигнала управления может произойти только после того, как МК изменит в результате обработки прерывания один из выходных сигналов RS-232, а это изменение должно быть в конце подпрограммы обработки прерывания, то длительность сигнала IRQ должна быть более продолжительная по времени выполнения команды RTI, т.е. более 21 машинного цикла или 10,5мкс, с двойным запасом получим 30мкс.

Перейдем к рассмотрению входных ПУ.

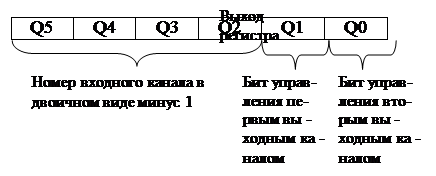

Как известно, уровни сигналов RS-232 составляют: «0» от –15В до –5В, «1» от +5В до+15В, а уровни КМОП 5В: «0» от –0,4В до +0,8В, «1» от +3,5В до +5,4В. схема входного ПУ представлена на рисунке 2.

Как известно, уровни сигналов RS-232 составляют: «0» от –15В до –5В, «1» от +5В до+15В, а уровни КМОП 5В: «0» от –0,4В до +0,8В, «1» от +3,5В до +5,4В. схема входного ПУ представлена на рисунке 2.

![]()

![]()

![]()

![]()

![]()

При подаче на вход ПУ напряжения более +5В диод VD1 откроется и через него и резистор R1 потечет ток, такой чтобы на выходе ПУ в результате падения на резисторе R1 напряжение составляло +5В+UVD . Где UVD – падение напряжения на диоде VD1, которое зависит от тока через него протекающего (чем меньше ток, тем меньше UVD, для малых токов на нижней части ВАХ диода), но UVD не может превышать 0,4В для относительно больших токов. Т.к. выходной ток ИС КР1554 составляет доли мкА, чтобы уменьшить UVD резистор R1 выбран относительно большим 1 МОм.

При подаче на вход ПУ напряжения более +5В диод VD1 откроется и через него и резистор R1 потечет ток, такой чтобы на выходе ПУ в результате падения на резисторе R1 напряжение составляло +5В+UVD . Где UVD – падение напряжения на диоде VD1, которое зависит от тока через него протекающего (чем меньше ток, тем меньше UVD, для малых токов на нижней части ВАХ диода), но UVD не может превышать 0,4В для относительно больших токов. Т.к. выходной ток ИС КР1554 составляет доли мкА, чтобы уменьшить UVD резистор R1 выбран относительно большим 1 МОм.

Аналогично ПУ работает при напряжении на входе меньше 0В ( ток течет через диод VD2).

Диоды VD1, VD2 являются встроенными защитными диодами ИС КР1554.

Резисторы R1…R5 необходимы для того, чтобы при отсутствии входных сигналов RS-232 входы ИС DD1.1 не оказались не подключенными, что не допустимо для КМОП ИС.

Выходные ПУ построены на ОУ DA1.1, DA1.2, DA2.1 включены по схеме компаратора с напряжением сравнения, формируемом на резистивных делителях R15R16, R18R19, R21R22, равным примерно 2,5В. резисторы R17, R20, R23 применены для защиты выходов ОУ от КЗ.

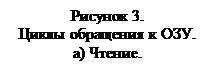

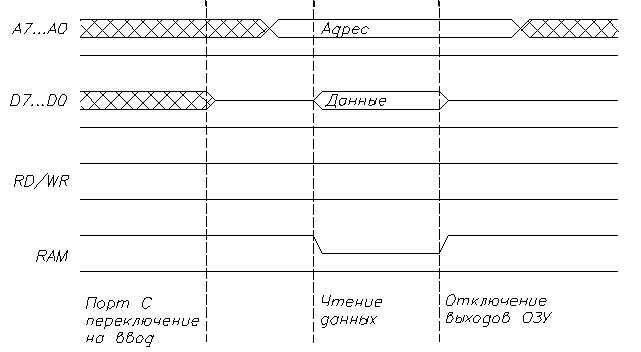

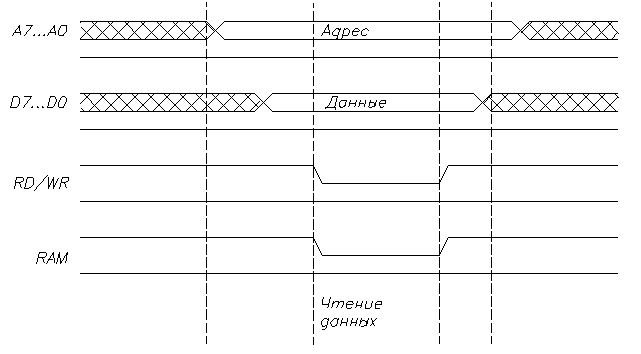

3) Оперативное запоминающее устройство.

|

Адресные входы ОЗУ DD10 подключены к шине адреса А7…А0 (порт А МК), входы/выходы данных DD10 подключены к шине данных D7…D0 (порт С). Всегда, кроме времени обращения МК к ОЗУ, сигналы RD/WR, подключенный к соответствующему входу DD10 (линия РВ2) и RAM, подключенный к входам «выбора ИС» (СЕ) и «разрешения выходов» (ОЕ) (линия РВ1) должны находиться в состоянии логической «1», т.е. выходы DD10 отключены от шины данных.

|

Циклы обращения к ОЗУ представлены на рисунке 3.

4) Цифроаналоговый преобразователь (ЦАП).

Блок ЦАП состоит непосредственно из самой ИС ЦАП DD12 с выходным ОУ DA3.2 и схемы формирования опорного напряжения. Схема формирования опорного напряжения состоит из параметрического стабилизатора R3VD1 с напряжением стабилизации 10В и масштабирующего усилителя на ОУ DA3.1 и R31…R33, с помощью подстроечного резистора R32 опорное напряжение должно регулироваться в пределах от –5В до минимального выходного напряжения ОУ –13В. Резистор R34 предназначен для защиты ОУ DA3.2 от КЗ.

Необходимо отметить, что т.к. на два младших разряда ЦАП всегда подан низкий уровень, то на выходе ЦАП максимальное напряжение не будет достигать опорного напряжения.

Запись цифрового кода во внутренний регистр DD12 происходит следующим образом:

МК выставляет на шину данных D7…D0 (PC7…PC0) младший байт кода, затем выставляются два старших разряда кода на D9, D8 (PB7, PB6) и одновременно сигнал D/A (PB3) переводится в высокий уровень, на выходе ЦАП появляется аналоговый сигнал соответствующий цифровому коду, чтобы «защелкнуть» код во входном регистре DD12 необходимо перевести сигнал D/A в низкий уровень, не изменяя сигналы на D8, D9.

Следует заметить, что во время обращения к ЦАП до «защелкивания» данных необходимо запрещать внешние прерывания, т.к. для регистра выходов RS-232 также используются линии D8, D9.

5) Выходные дискретные сигналы.

Выходные дискретные сигналы записываются в регистры DD13, DD14 следующим образом:

МК выставляет необходимые данные на линии D7…D0 (порт С), а затем на линии D8, D9 (PB6, PB7) и одновременно уровень логического «0» на линию OUT (PB4), после этого не изменяя данных, сигнал OUT переводится в логическую «1». Также как в случае с ЦАП необходимо запрещать внешние прерывания до перехода OUT в высокий уровень.

Выходы регистров DD13, DD14 являются выходными дискретными сигналами ТТЛ, т.к. выходные уровни КМОП 5В согласуются с входными уровнями ТТЛ, а выходной ток ИС серии КР1554 достаточно велик (до 20мА).

5. Литература.

1. Микросхемы для бытовой радиоаппаратуры. Справочник. Новаченко И.В. и др. – М.: Радио и связь, 1989г.

2. Интегральные микросхемы: Микросхемы для аналого-цифрового преобразования и средств мультимедиа. Выпуск 1. – М.: ДОДЭКА, 1996г.

3. Проектирование импульсных и цифровых устройств радиотехнических систем. Под ред. Казаринова Ю.М. – М.: Высшая школа, 1985г.

4. Потемкин И.С. функциональные узлы цифровой автоматики. – М.: Энергоатомиздат, 1988г.

5. Зельдин Е.А. цифровые интегральные микросхемы в информационно-измерительной аппаратуре. – Л.: Энергоатомиздат, 1986г.

6. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах. Справочник. – М.: Радио и связь, 1990г.

7. Уильямс Г.Б. Отладка микропроцессорных систем. – М.: Энергоатомиздат, 1988г.

8. Шило В.Л. Популярные цифровые микросхемы. Справочник. – М.: Радио и связь, 1988г.

9. Цифровые интегральные микросхемы. Справочник. Мальцев П.П. и др. – М.: Радио и связь, 1994г.

10. Логические интегральные схемы КР1553, КР1554. Справочник. – ТОО «БИНОМ», 1993г.

11. Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ. Справочник. - М.: Машиностроение, 1993г.

12. Разработка и оформление конструкторской документации радиоэлектронной аппаратуры. Справочник. Под ред. Романычевой Э.Т. – М.: Радио и связь, 1989г.